## **High-Performance IT Systems**

Dr. Tobias Kenter

## **FPGA Acceleration of Shallow Water Simulations**

## Bachelor/Master Thesis

In a Nutshell

- Understand performance critical parts of existing simulation code

- Extract functionality into OpenCL kernels

- Optimize kernels for FPGA design generation

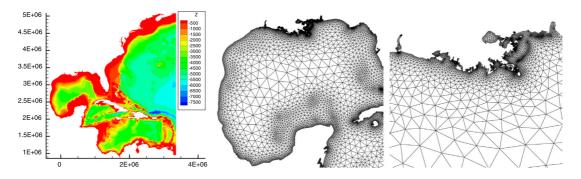

Understanding wave propagation in shallow waters, for example in the Caribbean sea is an important task, for example for tsunami warning systems and climate predictions. As the utilized simulation methods and models get more accurate, the computational requirements increase significantly. Novel accelerator technologies need to be explored to keep up with this demand. Recently, FPGAs have been shown to be a promising accelerator type for similar simulation methods from the physics domain.

In this thesis project, you will accelerate an existing shallow water simulation code for 2D wave propagation. The main code developer at Alfred Wegener Institute (AWI) in Bremerhaven is highly interested in this project and offers support to get started, for example through a short stay at AWI. At the Paderborn Center for Parallel Computing, we provide the state-of-the-art FPGA infrastructure and experience with the OpenCL design tools for FPGAs.

After extraction of performance critical code parts and functional integration of FPGAs through OpenCL, the focus of this thesis will be on the optimization of the generated FPGA designs. Though technically this involves just some code transformations and the addition of attributes to guide the compiler, a systematic approach requires to understand the transformation process from OpenCL code to FPGA circuits. Performance and resource models will be employed to further guide the optimization process. For a Master's project, an additional scientific aspect will be investigated, for example analyzing the interplay between algorithm parameters and hardware efficiency, or the impact of numeric precision of operands and operations on hardware utilization and convergence rates.

## **Supervisor:**

Tobias Kenter, Phone: 05251/60-4340 E-Mail: kenter@uni-paderborn.de