FPGA-basiertes System zur Erkennung von Gebärdensprache

- Systementwurfs-Teamprojekt für Computer Engineering Studenten

- Semester: Winter 2023/24

- Weitere Informationen: Folien vom Vorstellungsevent (werden noch hochgeladen)

Hintergrund

Maschinelles Sehen durch neuronale Netze hält Einzug in immer mehr Einsatzbereiche, darunter auch die automatische Erkennung von Gebärdensprache anhand von Videoaufnahmen. Diese Anwendung stellt jedoch besondere Anforderungen an das Erkennungssystem, da eine Echtzeit-Ausführung nötig ist und als Plattform oft eingebettete Systeme zum Einsatz kommen, welche ein limitiertes Energie- bzw. Rechenleistungsbudget aufweisen. Field Programmable Gate Arrays (FPGAs) können sich hier als ideale Plattform zur Hardwarebeschleunigung erweisen, da die Architekturen von neuronalem Netz und Prozessor aufeinander abgestimmt werden können. Hierzu forscht unsere Arbeitsgruppe im Rahmen des FINN Frameworks an Werkzeugen, mit denen approximierte neuronale Netze Schicht-für-Schicht in eine FPGA Prozessorarchitektur überführt werden können. Vergangene studentische Arbeiten demonstrierten diese Technologie bereits für die Erkennung von Gebärdensprache auf Basis von synthetischen Daten, jedoch ohne die vollständige Entwicklung eines Ende-zu-Ende Systems mit dem die Anwendung in Echtzeit demonstriert werden kann.

Projektziele

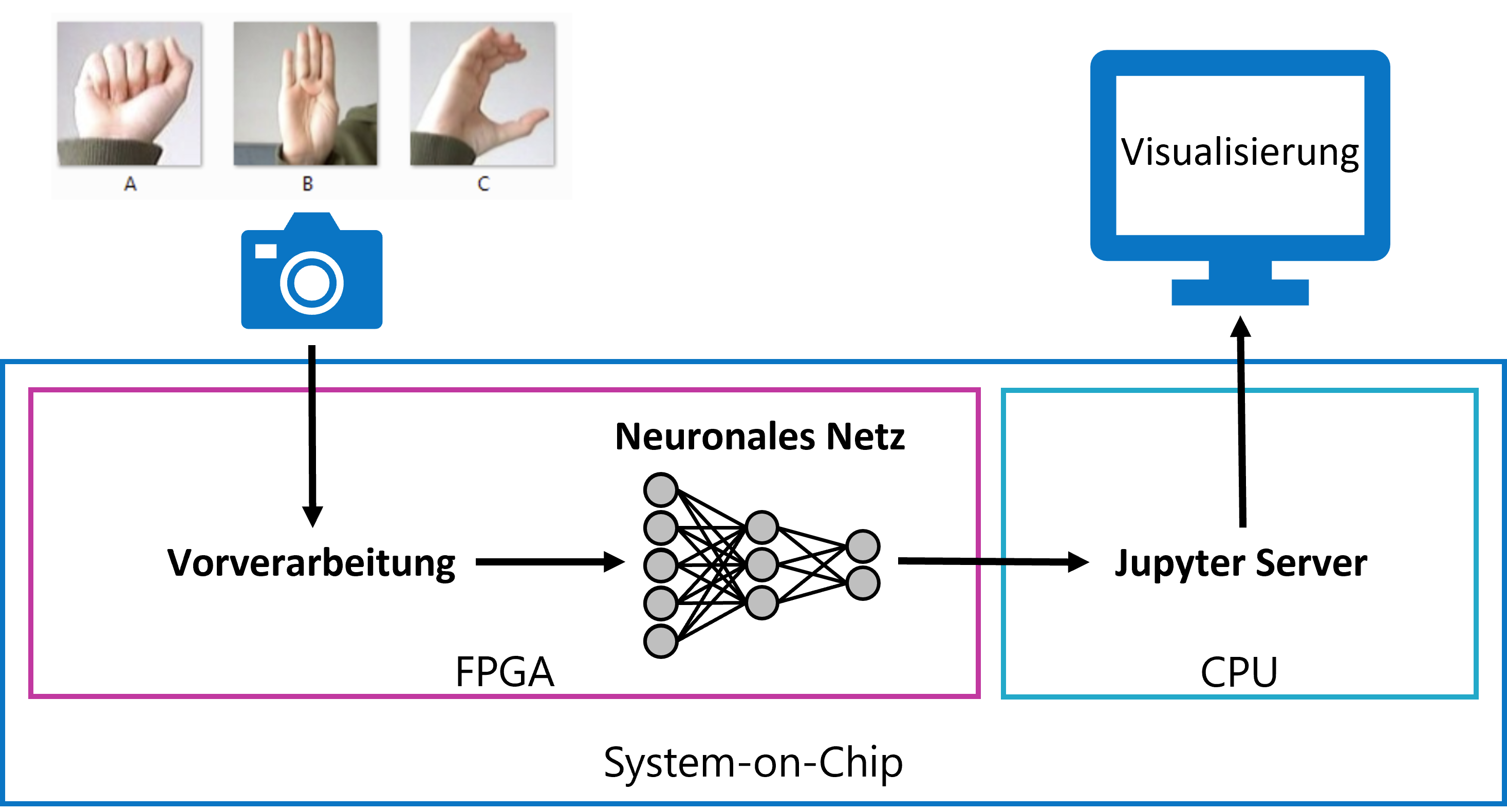

In diesem Projekt soll ein vollständiges FPGA-basiertes Videoverarbeitungssystem für die Erkennung von Gebärdensprache durch neuronale Netze entwickelt werden. Je nach Interesse und Fähigkeiten der Teilnehmer kann der Fokus auf die Vorverarbeitung des Datenstroms, den neuronalen Beschleuniger, oder die Visualisierung gelegt werden. Das System wird auf einem AMD/Xilinx Entwicklungsboard mit ZYNQ System-on-Chip (SoC) implementiert, welches ARM CPU Kerne, programmierbare FPGA Logik und Anschlussmöglichkeiten für Peripheriegeräte bietet. Die folgenden Aufgaben sollten implementiert, bzw. integriert werden:

- Videoübertragung von einer (HDMI) Kamera

- Vorverarbeitung des Videostreams um Auflösung, Farbraum, Bildrate, etc. anzupassen

- Verarbeitung des Videostreams durch einen FINN-generierten Beschleuniger für das neuronale Netz

- Kommunikation und Visualisierung der Ergebnisse über einen Monitor oder ein Web-basiertes Jupyter System

Lernziele

In diesem Projekt steht effektive Teamarbeit im Vordergrund. Zusätzlich können erste Erfahrungen in der Programmierung von FPGAs und Treibern gesammelt werden:

- Organisation im Team

- Werkzeuge für die Zusammenarbeit (z.B. Git für Versionskontrolle)

- Software-Programmierung mit Python und Jupyter

- FPGA-Programmierung mit C/C++ basierter High-Level Synthese (HLS) und entsprechenden Bibliotheken

- Optional: Einblick in das Training und die Beschleunigung von quantisierten neuronalen Netzen